|

|

|

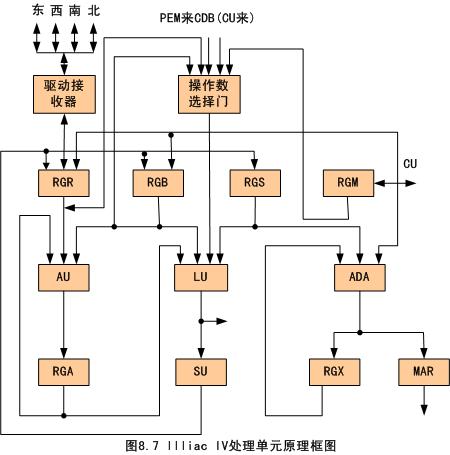

处理单元的原理框图如图8.7所示。它有6个可编程序寄存器RGA、RGB、RGR、RGS、RGX和RGM,以及加/乘算术单元AU、逻辑单元LU、移位单元SU和地址加法器ADA等。RGA是累加寄存器,存放第一操作数和操作结果;RGB是操作数寄存器,存放加、减、乘、除等二元操作的第二操作数;RGR是被乘数寄存器兼互连寄存器,经过东、西、南、北四个互连路径之一完成处理单元之间的数据直接交往;RGS是通用寄存器,可被程序用来暂存中间结果。这四个寄存器都是64位的。操作数来自以下四个方面:PE本身的寄存器;阵列存储器;CU的公共数据总线;PE的四个近邻。16位的RGX是变址寄存器,它利用地址加法器ADA修改指令地址,并将形成的有效地址经过存储器地址寄存器MAR输往存储器逻辑部件MLU。最后是8位的模式寄存器RGM,它的E和E1位是"活动"标志位,F和F1位保存运算结果出错(上溢、下溢)标志,G、H、I、J位保存测试结果。RGM经常处于CU的监督之下,一旦出错,就发出CU陷阱中断。模式寄存器的活动标志位E和E1用来控制RGA、RGS和阵列存储器的工作,E还控制RGX。当PE以32位字长运算时,E和E1是互相独立的。活动标志位的设立使对64个处理单元中的每一个处理单元都可以进行单独控制。只有那些处于活动状态的处理单元才执行单指令流规定的共同操作。RGM处于程序员的控制之下,可根据其它几个寄存器的内容置为"活动"或"不活动"状态。例如,有一种指令就能在RGR的内容大于RGA的内容时置该处理单元为"不活动"状态。模式寄存器在阵列处理机中是必不可少的,它对增强阵列处理机的功能和结构灵活性发挥着很大的作用。

阵列存储器的另一个特点是它的双重变址机构:控制器实现所有处理单元的公共变址,每一个处理单元内部还可以单独变址。最终的操作数有效地址对 |