|

|

|

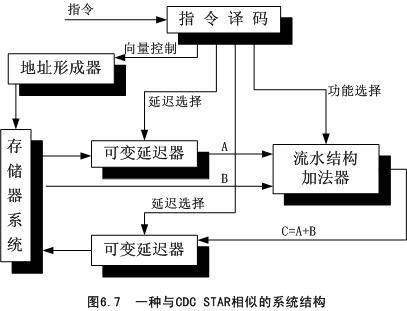

图6.7是实现这种思想的方框图。它与70年代中期制造的巨型机CDCSTAR的结构相似。图中一条输入数据通路和结果数据通路分别加了可变延迟。其延迟时间可根据输入向量和结果向量的第一个元素的位置来设置。这样,在经过初始化阶段后,流水线将以全速运行。然而,如果向量较短,而延迟时间较长,则会严重影响系统的性能。 指令译码器根据向量的起始地址和流水结构运算器执行的具体操作的吞吐率设置延迟的大小。地址生成器形成指令执行过程中要存取的数据的地址。

图6.7中的算术运算子系统的功能可以选择。CDCSTAR不能重叠地进行两种或多种向量运算,因此不同的向量操作可以共享共同的运算部件。例如,浮点加和浮点乘就可以使用同一个硬件进行阶码相加、移位以及尾数相加。

|